SDLS104 - OCTOBER 1976 - REVISED MARCH 1988

- Four J-K Flip-Flops in a Single Package . . .

Can Reduce FF Package Count by 50%

- Common Positive-Edge-Triggered Clocks with Hysteresis . . . Typically 200 mV

- Fully Buffered Outputs

- Typical Clock Input Frequency . . . 45 MHz

### description

These quadruple TTL J- $\vec{k}$  flip-flops incorporate a number of third-generation IC features that can simplify system design and reduce flip-flop package count by as much as 50%. They feature hysteresis at the clock input, fully buffered outputs, and direct clear capability. The positive-edge-triggered SN54376 and SN74376 are directly compatible with most Series 54/74 MSI registers.

The SN54376 is characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C; the SN74376 is characterized for operation from 0°C to 70°C.

FUNCTION TABLE (EACH FLIP-FLOP)

| COMMON INPUTS |       | INP | UTS | OUTPUT         |  |  |

|---------------|-------|-----|-----|----------------|--|--|

| CLEAR         | CLOCK | J   | ĸ   | ٩              |  |  |

| L             | х     | X   | X   | L              |  |  |

| н             | 1     | L   | Н   | Ω <sub>0</sub> |  |  |

| Н             | 1     | н   | н   | н              |  |  |

| н             | Ť     | L   | L   | L              |  |  |

| н             | t     | н   | L   | TOGGLE         |  |  |

| н             | L     | X   | X   | 0 <sub>0</sub> |  |  |

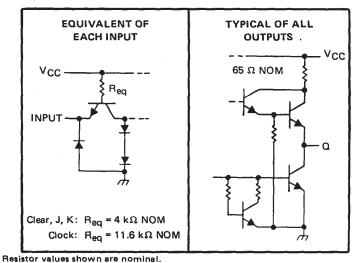

#### schematics of inputs and outputs

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

| SN54376 J PACKAGE<br>SN74376 N PACKAGE<br>(TOP VIEW) |   |    |     |  |  |  |  |  |  |

|------------------------------------------------------|---|----|-----|--|--|--|--|--|--|

|                                                      |   |    |     |  |  |  |  |  |  |

| 1J                                                   | 2 | 15 |     |  |  |  |  |  |  |

|                                                      | 3 | 14 |     |  |  |  |  |  |  |

| 10                                                   | 4 | 13 |     |  |  |  |  |  |  |

| 20                                                   | 5 |    |     |  |  |  |  |  |  |

|                                                      | 5 | 12 |     |  |  |  |  |  |  |

| 2K                                                   | Б | 11 | 5   |  |  |  |  |  |  |

| 2J                                                   | 7 | 10 | Цзј |  |  |  |  |  |  |

| GND                                                  | 8 | 9  |     |  |  |  |  |  |  |

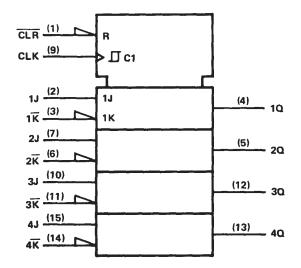

logic symbol<sup>†</sup>

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.

# SN54376, SN74<u>37</u>6 QUADRUPLE J-K FLIP-FLOPS

SDLS104 - OCTOBER 1976 - REVISED MARCH 1988

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)  |                |

|-----------------------------------------------|----------------|

| Input voltage                                 | 5.5 V          |

| Operating free-air temperature range: SN54376 | -55°C to 125°C |

| SN74376                                       | 0°C to 70°C    |

| Storage temperature range                     | -65°C to 150°C |

NOTE 1: Voltage values are with respect to network ground terminals.

### recommended operating conditions

|                                    |                      | SN54376 |     | SN74376 |      |     |      |     |

|------------------------------------|----------------------|---------|-----|---------|------|-----|------|-----|

|                                    |                      | MIN     | NOM | MAX     | MIN  | NOM | MAX  |     |

| Supply voltage, V <sub>CC</sub>    |                      | 4.5     | 5   | 5.5     | 4.75 | 5   | 5.25 | V   |

| High-level output current, IOH     |                      |         |     | -800    |      |     | -800 | μA  |

| Low-level output current, IOL      |                      |         |     | 16      |      |     | 16   | mA  |

| Clock frequency                    |                      | 0       |     | 30      | 0    |     | 30   | MHz |

| Pulse width, t <sub>W</sub>        | Clock high           | 22      |     |         | 22   |     |      |     |

|                                    | Clock low            | 12      |     |         | 12   |     |      | ns  |

|                                    | Preset or clear low  | 12      |     |         | 12   |     |      |     |

| Setup time, t <sub>su</sub>        | J, K inputs          | 10      | :   |         | 01   |     |      | ns  |

|                                    | Clear inactive state | 10†     |     |         | 10†  |     |      | 113 |

| Input hold time, th                |                      | 20†     |     |         | 201  |     |      | ns  |

| Operating free-air temperature, TA |                      | - 55    |     | 125     | 0    |     | 70   | °C  |

↑↓The arrow indicates the edge of the clock pulse used for reference: ↑ for the rising edge, ↓ for the falling edge,

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                                        | TEST CONDITIONS <sup>†</sup>                       |                                                     | MIN | TYP‡ | MAX  | UNIT |

|-----------------|----------------------------------------|----------------------------------------------------|-----------------------------------------------------|-----|------|------|------|

| VIH             | High-level input voltage               |                                                    |                                                     | 2   |      |      | V    |

| VIL             | Low-level input voltage                |                                                    |                                                     |     |      | 0.8  | V    |

| VIK             | Input clamp voltage                    | V <sub>CC</sub> = MIN,                             | l <sub>l</sub> = –12 mA                             |     |      | -1.5 | V    |

| VOH             | High-level output voltage              | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>1H</sub> = 2 V,<br>I <sub>OH</sub> = -800 μA | 2.4 | 3.4  |      | v    |

| VOL             | Low-level output voltage               | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OL</sub> = 16 mA   |     | 0.2  | 0.4  | v    |

| 4               | Input current at maximum input voltage | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5.5 V                              |     |      | 1    | mA   |

| ТН              | High-level input current               | $V_{CC} = MAX,$                                    | VI = 2.4 V                                          |     |      | 40   | μA   |

| 1 <sub>IL</sub> | Low-level input current                | $V_{CC} = MAX,$                                    | V <sub>1</sub> = 0.4 V                              |     |      | -1.6 | mA   |

| los             | Short-circuit output current§          | V <sub>CC</sub> = MAX                              |                                                     | -30 |      | 85   | mA   |

| ICC             | Supply current                         | V <sub>CC</sub> = MAX                              |                                                     |     | 52   | 74   | mA   |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

<sup>‡</sup>All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

\$Not more than one output should be shorted at a time.

### switching characteristics, $V_{CC}$ = 5 V, $T_A$ = 25°C

|                  | PARAMETER                                                   | TEST CONDITIONS | MIN | ТҮР | MAX | UNIT |

|------------------|-------------------------------------------------------------|-----------------|-----|-----|-----|------|

| f <sub>max</sub> | Maximum clock frequency                                     | CL = 15 pF,     | 30  | 45  |     | MHz  |

| TPHL             | Propagation delay time, high-to-low-level output from clear |                 |     | 17  | 30  | ns   |

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level output from clock | See Note 2      |     | 22  | 35  | ns   |

| TPHL             | Propagation delay time, high-to-low-level output from clock | See Note 2      |     | 24  | 35  | ns   |

NOTE 2: Load circuits and voltage waveforms are shown in Section 1.